Author Affiliations

Abstract

1 School of Electronics and Information, Hangzhou Dianzi University, Hangzhou 310018, China

2 Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology, School of Microelectronics, Tianjin University, Tianjin 300072, China

3 Chongqing Optoelectronics Research Institute, Chongqing 400060, China

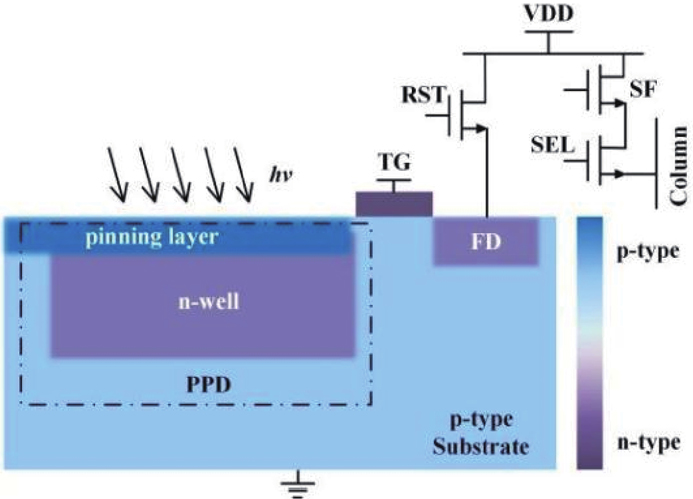

CMOS image sensors produced by the existing CMOS manufacturing process usually have difficulty achieving complete charge transfer owing to the introduction of potential barriers or Si/SiO2 interface state traps in the charge transfer path, which reduces the charge transfer efficiency and image quality. Until now, scholars have only considered mechanisms that limit charge transfer from the perspectives of potential barriers and spill back effect under high illumination condition. However, the existing models have thus far ignored the charge transfer limitation due to Si/SiO2 interface state traps in the transfer gate channel, particularly under low illumination. Therefore, this paper proposes, for the first time, an analytical model for quantifying the incomplete charge transfer caused by Si/SiO2 interface state traps in the transfer gate channel under low illumination. This model can predict the variation rules of the number of untransferred charges and charge transfer efficiency when the trap energy level follows Gaussian distribution, exponential distribution and measured distribution. The model was verified with technology computer-aided design simulations, and the results showed that the simulation results exhibit the consistency with the proposed model.

CMOS image sensor charge transfer interface state traps Journal of Semiconductors

2023, 44(11): 114104

1 重庆光电技术研究所,重庆 400060

2 天津大学 微电子学院,天津 300072

针对3D集成式多光谱TDI-CMOS图像传感器的数字化处理和高速读出需求,为了解决与TDICCD探测器的整体布局、物理尺寸和接口的匹配性和一致性问题,研制了适用于五谱段TDICCD的CMOS读出电路芯片。该读出电路芯片创新地设计了一种使用多相位ADC时钟、支持相关多次采样的新型列级单斜ADC电路结构,实现了TDICCD信号的数字化和高速输出,有效提升了探测器的动态范围和噪声指标。流片测试结果表明:读出电路芯片的功能正常,集成式TDICCD的成像效果良好,新型列级ADC工作正常,读出电路以最小9.5 μs的行周期输出14 bit数据,相关多次采样具备降低输出信号噪声的作用,实现了TDICCD信号的高精度数字化处理和高速输出,满足3D集成式TDI-CMOS图像传感器的研制要求。

CMOS读出电路 多光谱TDICCD 芯片3D集成 单斜ADC 相关多次采样 CMOS readout circuit multispectral TDICCD 3D integration of IC single-slope ADC correlated multiple sampling

1 中国电子科技集团公司第十一研究所, 北京 100016

2 重庆光电技术研究所, 重庆 400060

3 天津大学 微电子学院, 天津 300072

针对高帧频、全局曝光、通道数可选等成像应用需求,提出了一种高光谱成像用CMOS图像传感器,重点分析了8T像素结构和读出电路的设计方案与电路原理,完成了芯片的整体仿真和流片验证。结果表明:设计符合预期,成像效果良好,像素具备较高的满阱和全局快门功能,读出电路实现了输出通道数可选功能,同时保证了模拟信号在大面阵、低输出通道数条件下的高速、低噪声输出,最终实现的像素阵列为2048×256,像素尺寸为24μm×24μm,单通道最大输出频率为40×106pixel/s,最高帧频为4000f/s,可满足高光谱成像系统对图像传感器的需求。

CMOS图像传感器 高光谱成像 全局快门 高帧频 CMOS image sensor hyperspectral imaging global shutter high frame rate

太空环境中的电离辐射会导致CMOS图像传感器性能退化, 甚至造成永久性损毁。文章对CMOS图像传感器抗电离辐射加固技术进行了研究, 从版图设计、电路设计等方面提出相应的抗辐射策略, 并进行了总剂量和单粒子试验。试验结果表明, 采用抗辐射加固技术设计制作的CMOS图像传感器具备抗总剂量和单粒子辐射能力, 当总剂量达到100krad(Si)、单粒子辐射总注量达到1×107p/cm2时, 器件的关键指标变化符合预期要求。

CMOS图像传感器 抗电离辐射加固 总剂量效应 单粒子 CMOS image sensor radiation-hardening total dose effect single event effects

1 重庆光电技术研究所, 重庆 400060

2 中国科学院重庆绿色智能技术研究院, 重庆 400714

为了解决石墨烯探测器光电探测的难题, 针对石墨烯探测器受光照像元电阻发生变化的特点, 设计了基于石墨烯探测器的新型积分电路结构。该积分电路结构主要包含前端偏置电路、运算放大器以及开关和反馈电容等部分, 电路主要利用暗像元电阻不随光照变化, 而感光像元电阻会随光照强度变化而变化的特点, 将光照条件下暗像元支路的电流与感光像元支路电流的差作为光响应电流, 并采用CTIA积分电路进行电流积分, 将光响应电流转换为积分电压输出, 进而实现石墨烯探测器对光响应信号的探测和输出。文中对相关的主要电路设计进行了分析, 并基于Cadence ADE仿真环境完成了电路仿真。经仿真分析, 基于文中的积分电路, 可以将不同光照条件下石墨烯探测器的光响应转换为对应的积分电压输出。可见, 所设计的积分电路能够满足石墨烯探测器对光响应探测的需求, 对石墨烯材料进入光电探测器领域具有重要意义。

石墨烯 探测器 近红外 积分电路 graphene detector near-infrared integration circuit

为满足CMOS图像传感器(CIS)图像数据高速输出的需求, 提出一种适用于CIS的片上高速低电压差分信号(LVDS)驱动电路结构。首先介绍了CIS高速数据传输接口的常见类型、LVDS接口技术的起源和特点; 接着根据CIS的需求特点确定了LVDS驱动电路的设计思路和结构; 最后给出了驱动电路设计原理图和仿真结果, 以及接收端眼图仿真结果。仿真结果表明,该LVDS驱动电路, 数据传输速率可以达到500Mb/s, 所有参数均满足TIA/EIA644A接口标准的需求, 接收端眼高为310mV, 眼宽为0.9UI。

CMOS图像传感器 LVDS驱动电路 TIA/EIA644A接口标准 眼图 CMOS image sensor LVDS driver circuit TIA/EIA644A standard eye diagram

随着CMOS图像传感器(CIS)的广泛应用, 低功耗、高集成化、高稳定性成为其发展趋势, 低压差线性稳压器(LDO)因体积小、功耗低、噪声低及电源抑制比高等优点而满足芯片供电需求。为了避免传统电源在芯片异常时仍持续工作致使功耗增加或芯片烧毁, 设计了一种可应用于CMOS图像传感器的LDO电路, 并加入了LDO的保护电路结构。该保护电路具有欠压保护与过流保护的功能, 并能够通过数字电路对LDO进行使能控制。基于0.11μm CMOS工艺平台对LDO及其保护电路进行仿真与分析, 完成了该工艺下电路版图的绘制和验证。

保护电路 欠压保护 过流保护 CIS CIS LDO LDO protection circuit undervoltage protection over current protection

1 中国电子科技集团公司第十一研究所, 北京 100015

2 重庆光电技术研究所, 重庆 400060

3 重庆大学 通信工程学院, 重庆 400044

针对图像在传输过程中易引入噪声、色彩质量下降、中值滤波导致图像细节丢失和均值滤波出现模糊等问题, 提出了一种可以应用于CMOS图像传感器的图像画质增强和滤波算法。该算法对插值后的Bayer图像数据进行一维空间的增强和降噪处理, 首先将图像从RGB空间转换到YUV空间, 在Y通道上用改进的直方图均衡化方法实现图像明暗程度的对比度增强调节, 对U、V通道采用分段式线性调节方法实现饱和度调节; 然后对Y通道进行自适应降噪, 对U、V通道进行加权中值滤波降噪, 以满足后续处理对图像质量的要求; 最后在Y通道上, 采用基于Laplace算子的锐化掩模进行锐化处理, 保证图像的细节清晰可见。实验结果表明: 从图像视觉效果来看, 相比单独使用中值和均值滤波, 所提出的自适应滤波得到的效果更好, 图像细节保存较好、模糊程度低、图像更为清晰, 且色彩质量更高。通过对比峰值信噪比(PSNR), 对混合噪声进行处理时, 该滤波算法的PSNR优于中值和均值滤波, 有效地抑制了噪声。整个算法在一维邻域空间进行, 更容易在有限的硬件上实现较好的图像处理结果, 满足小面积低功耗的要求。

降噪滤波 CMOS图像传感器 饱和度 边缘增强 noise reduction filtering CMOS image sensor saturation edge enhancement

从方法优化和电路设计入手,提出了基于片上系统(SOC)的复位方法和时钟复位电路。设计了片外按键复位电路、片内上电电路、晶振控制电路、片内RC低频时钟电路、槽脉冲产生电路、分频延时电路、时钟切换电路及异步复位同步释放电路等电路模块。以上电路模块构成了片上系统的时钟复位电路,形成了特定的电路时钟复位系统。该时钟复位系统将片外按键复位与片内上电复位结合起来,形成多重复位设计,相比单纯按键复位更智能,相比单纯上电复位则更可靠。另外,该时钟复位系统还采用了片内RC振荡时钟电路等一系列电路,借助片内RC时钟实现对芯片的延时复位,进而在保证复位期间寄存器得到正确初始化的同时,还使得芯片能够始终处在稳定的晶振时钟下正常工作。相比传统的时钟复位电路,该时钟复位系统既便捷,又保证了系统初始化和系统工作的可靠性。

片上系统 时钟设计 复位设计 延时复位 system on chip clock design reset design timedelay reset

针对传统自动曝光算法难以兼顾实时性和平滑性的缺点,设计了一种结合直接计算法和可变步长调节法的综合性算法,研究了算法原理,给出了算法流程。该算法可以通过改变步长参数,自由设定将图像亮度调节到目标亮度的时间,使其能够适用于各种不同的应用场合。在基于FPGA的CMOS图像采集平台上完成了算法实现,实验结果证明采用该算法可以使图像亮度快速平稳地接近理想亮度,成像效果很好。

自动曝光 CMOS图像传感器 安防监控 auto exposure CMOS image sensor security monitoring